- AMD K10 ARCHITECTURE SERIAL

- AMD K10 ARCHITECTURE CODE

- AMD K10 ARCHITECTURE PC

- AMD K10 ARCHITECTURE SERIES

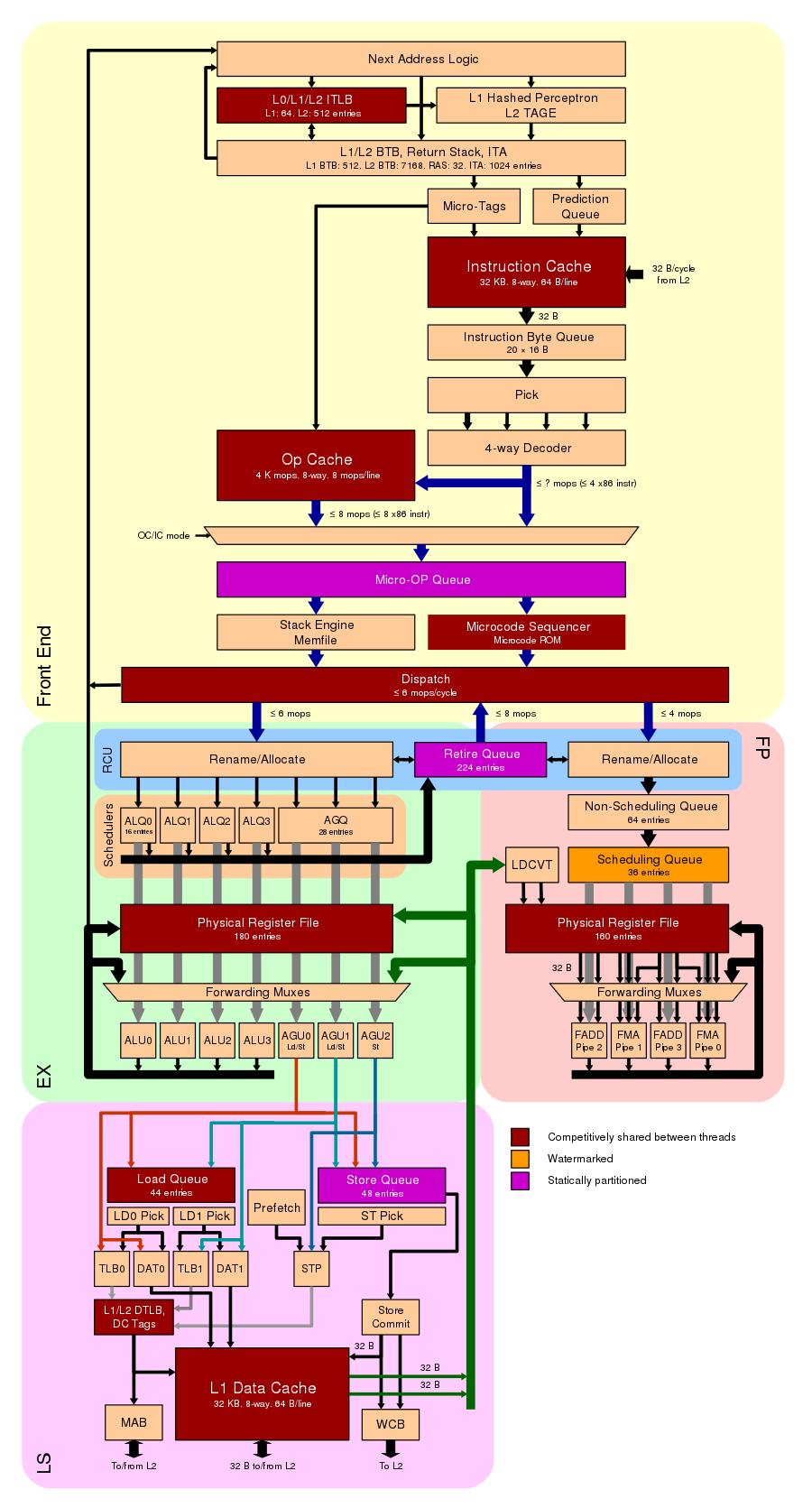

But most consumer workloads still can't be distributed evenly across eight threads. The high-end desktop parts, with their four modules and eight threads, had an abundance of integer threads. AMD designed the processor with a base clock speed goal of 4.4GHz. So, too, was the floating point pipeline, with two 128-bit fused multiply-add (FMA) units that could be paired together to perform a single 256-bit AVX FMA instruction. Compared to Bulldozer's predecessor, the K10, each integer pipeline was narrow: two arithmetic logic units (ALUs) and two address generating units (AGUs), instead of three of each in K10. Desktop processors shipped with two, three, or four modules for four, six, or eight threads in total.

AMD hoped all those threads would be working hard.Įach Bulldozer module could run two threads simultaneously, with two independent integer pipelines and one shared floating point pipeline within a module. The idea was that clock speed and the GPU would make up for the narrowness and lack of floating point capability. This platform illustrates AMD's leadership in developing a single solution with increased levels of integration to boost real-world performance.Further Reading Can AMD survive Bulldozer’s disappointing debut?Īccordingly, AMD created processors with oodles of simultaneous threads, relatively long pipelines, relatively narrow pipelines, and relatively few floating point resources. The demonstration platform includes two true quad-core AMD Phenom processors, the new DirectX 10 ATI Radeon HD 2900 XT, as well as an upcoming AMD next-generation, high-performance chipset, due in the second half of 2007. In a demonstration in San Francisco, AMD previewed an eight-core platform, codenamed "FASN8," pronounced "fascinate," to show the first AMD silicon-based next-generation eight-core platform. AMD expects true quad-core and dual-core AMD Phenom-based desktop systems will ship in the second half of 2007.

AMD K10 ARCHITECTURE PC

Delivering a four-core foreshadowing of innovations to come for PC enthusiasts worldwide, AMD (NYSE: AMD) today unveiled the upcoming AMD Phenom(tm) processor family name and publicly demonstrated the first all-AMD enthusiast platform, codenamed "FASN8." The industry's only true quad-core client processors are expected to deliver the ultimate visual experience, especially when paired with AMD's new DirectX 10 ATI Radeon(tm) HD 2000 series, which began shipping today (see related press release: "AMD Introduces the ATI Radeon(tm) HD 2000 Series, Delivering The Ultimate Visual Experience(tm) for Desktop and Mobile Platforms").

AMD K10 ARCHITECTURE SERIES

Industry's only true x86 quad-core architecture paired with theĪTI Radeon(tm) HD 2000 series to offer a phenomenal computing experience. Phenom FX, X4 and X2 processors are expected to be available toward the end of '07.ĪMD makes first public demonstration of all-AMD enthusiast platform codenamed "FASN8". Finally, through what AMD is calling their DSDC (Dual Socket Direct Connect) architecture, the new platform will enable 8-way octa-core system designs for the enthusiast and profressional workstation markets. The X2 obviously signifies a dual-core chip, while FX and X4 denote quad-core architectures.

AMD K10 ARCHITECTURE SERIAL

Regardless, since Barcelona will have faster on-off chip access with four serial HT links at its disposal, it's conceivable that these deficiencies can be mitigated somewhat.Īs you'll note in the above AMD slideware, Phenom processors will come in a variety of flavors, including an enthusiast class Phenom FX, the high-end Phenom X4 and mainstream Phenom X2.

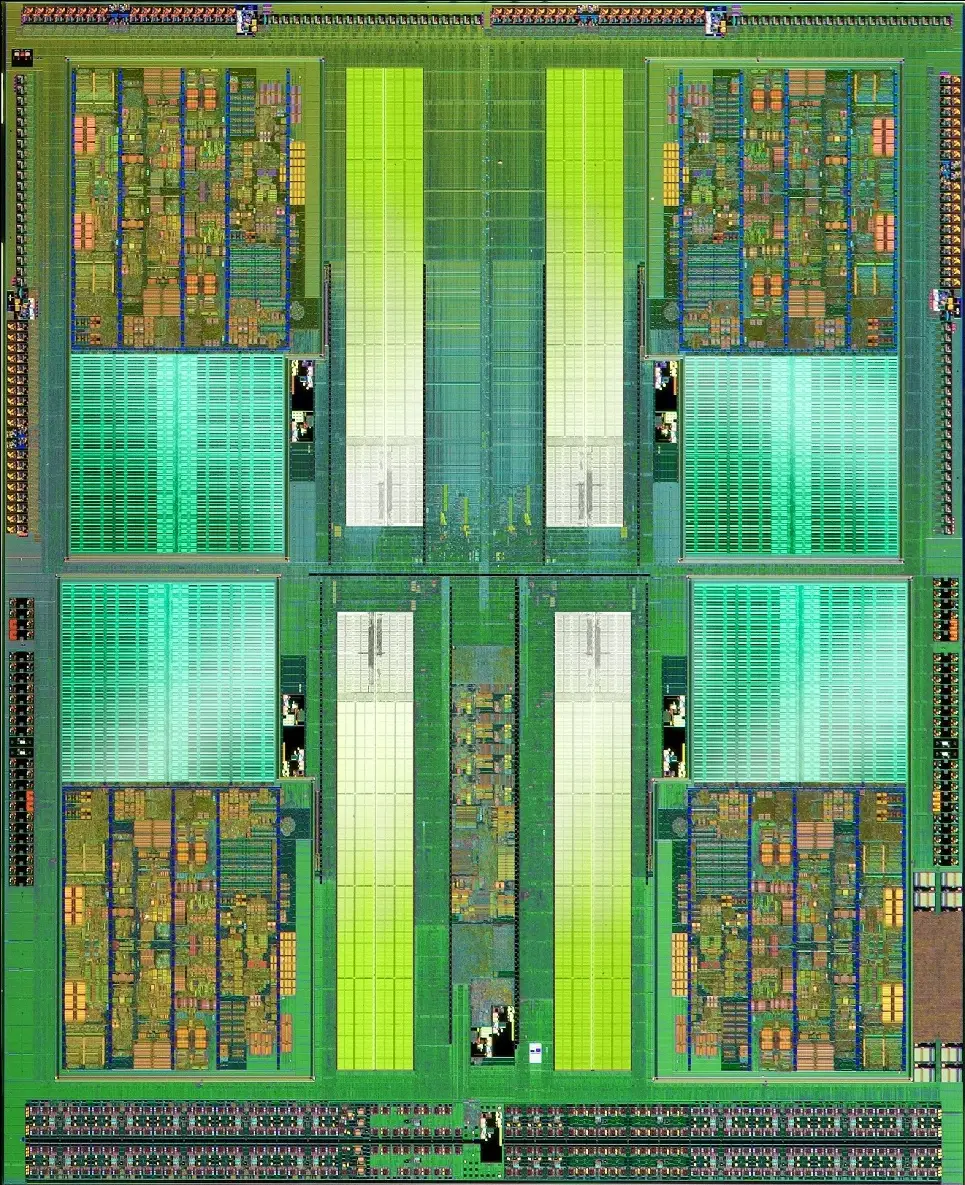

So while Intel is beefing up their cores with up to 8MB of shared L2 cache currently for Kentsfield and 12MB L2 for their upcoming Penryn chip, AMD is still conserving die area it seems, with only 4MB total on-chip cache. In addition to a faster on-die memory controller, the chip will support 64-bit and 128-bit SSE operations and come with 2MB of on-chip L2 cache (512KB dedicated per core) and 2MB of shared 元 cache. In addition, each core will have one of four Hypertransport links supporting it with AMD's Direct Connect Architecture that has higher throughput over traditional Front Side Bus architectures. The chip is built on AMD's 65nm process and is comprised of up to 4 32/64-bit capable CPU engines on a single die.

AMD K10 ARCHITECTURE CODE

Though leaks of the product have been circulating around the web for months now, today AMD is officially announcing their Phenom brand of processors based on their next generation K10 CPU core architecture, code named Barcelona.